IDT79R3081E

IDT79R3081E is RISController with FPA manufactured by Integrated Device.

- Part of the IDT comparator family.

- Part of the IDT comparator family.

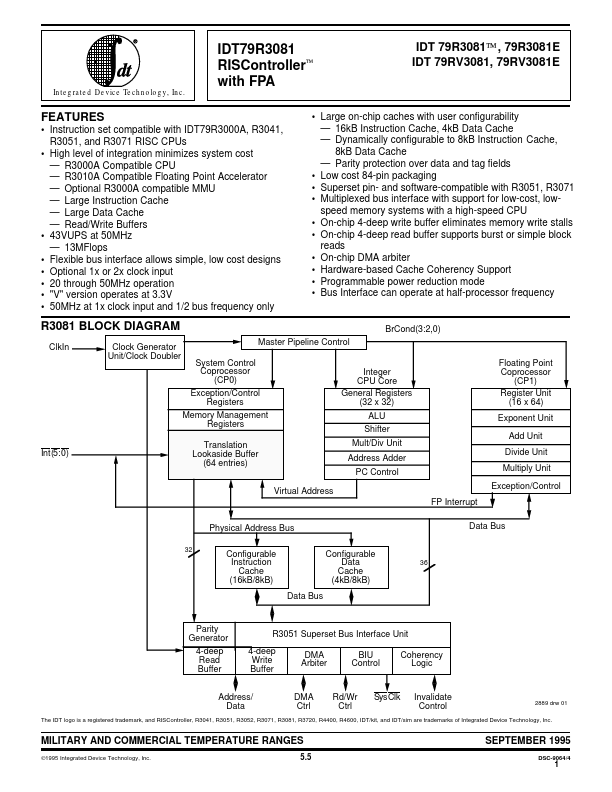

IDT79R3081 RISController

MILITARY AND MERCIAL TEMPERATURE RANGES

Integrated Device Technology, Inc.

IDT79R3081 RISController™ with FPA

IDT 79R3081™ , 79R3081E IDT 79RV3081, 79RV3081E

Features

- Instruction set patible with IDT79R3000A, R3041, R3051, and R3071 RISC CPUs

- High level of integration minimizes system cost

- R3000A patible CPU

- R3010A patible Floating Point Accelerator

- Optional R3000A patible MMU

- Large Instruction Cache

- Large Data Cache

- Read/Write Buffers

- 43VUPS at 50MHz

- 13MFlops

- Flexible bus interface allows simple, low cost designs

- Optional 1x or 2x clock input

- 20 through 50MHz operation

- "V" version operates at 3.3V

- 50MHz at 1x clock input and 1/2 bus frequency only

- Large on-chip caches with user configurability

- 16k B Instruction Cache, 4k B Data Cache

- Dynamically configurable to 8k B Instruction Cache, 8k B Data Cache

- Parity protection over data and tag fields

- Low cost 84-pin packaging

- Superset pin- and software-patible with R3051, R3071

- Multiplexed bus interface with support for low-cost, lowspeed memory systems with a high-speed CPU

- On-chip 4-deep write buffer eliminates memory write stalls

- On-chip 4-deep read buffer supports burst or simple block...